|

|

Advertisement:

|

|

Intel Core 2 Duo "Conroe" CPUs |

|

Join the community - in the OCAU Forums!

|

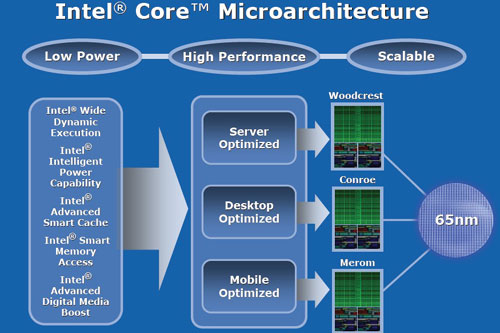

The "Core" Microarchitecture

The Core Microarchitecture:

As we will later show, Core 2 Duo is in every aspect a far better product than its NetBurst based predecessor Pentium D. We therefore think it is worthwhile to have a short look into the design features of the Core micro-architecture so as to understand the magic behind this achievement before we move to benchmarking and overclocking.

Intel is claiming several significant innovations for its Core micro-architecture, namely:- Wide Dynamic Execution

- Advanced Smart Cache

- Smart Memory Access

- Intelligent Power Capability

- Digital Media Boost

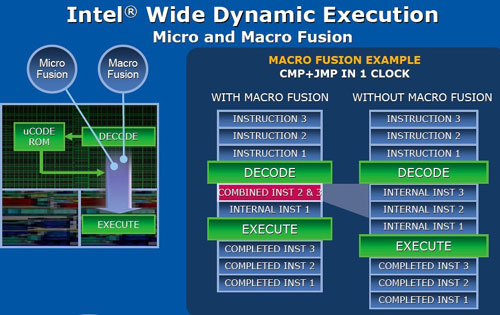

The Pentium 4 NetBurst micro-architecture is based on a deep, 32-stage pipeline execution engine that can handle 3 instructions at a time. Core comes with a 14-stage pipeline optimized by Wide Dynamic Execution. It improves execution speed and efficiency by delivering more instructions per clock cycle. Each core can complete now up to four full instructions simultaneously. In addition the execution time has been reduced by macrofusion. In previous generation processors each incoming instruction was individually decoded and executed. Macrofusion enables instruction pairs to be combined into a single instruction during decoding. Two program instructions can then be executed as one, reducing the amount of work the processor has to do.

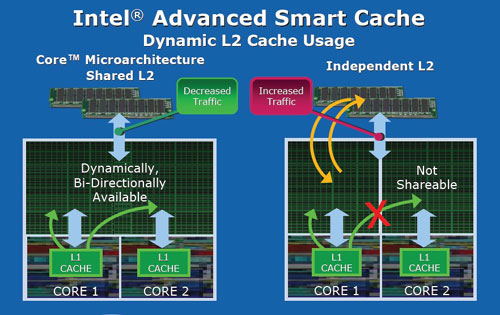

Advanced Smart Cache: Conroes shared L2 cache is dynamically allocated to each processor core based on workload. This increases the probability that each core can access data from fast L2 cache, significantly reducing latency to frequently used data and improving performance. To understand the advantage of this design consider that most current multi-core implementations do not share L2 cache. Conroes NetBurst based predecessor Presler also had 4 MB of total L2 cache, but each core could only access its own L2 cache of 2 MB each. The Core micro-architecture with a shared L2 cache allows each core to dynamically utilize up to 100% of the available 4 MB. When 1 core has no or minimal cache requirements, other core(s) are allowed to increase their percentage of L2 cache - reducing cache misses and increasing performance.

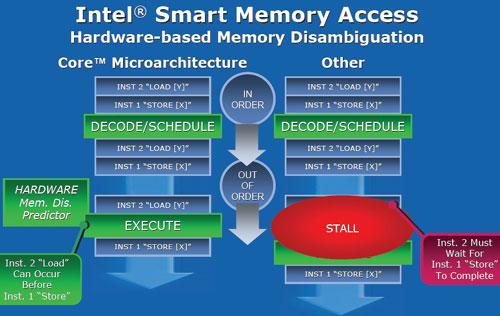

Smart Memory Access optimizes the use of the data bandwidth from the memory subsystem to accelerate out-of-order execution. A newly designed prediction mechanism reduces the time in-flight instructions have to wait for data. In their Core Microarchitecture whitepaper Intel mentions memory disambiguation and advanced pre-fetching in this context. These new algorithms make it possible that data are moved from system memory into fast L2 cache in advance of execution. This keeps the pipeline better filled, improving instruction throughput and performance.

The Core micro-architecture is executing 128-bit Streaming SIMD Extension (SSE) instructions at a throughput rate of one per clock cycle. This is effectively doubling their speed of execution on a per clock basis over previous generation processors. Intel is claiming that this will significantly improve the performance of video, audio, image and photo processing, multi-media, encryption, financial, engineering and scientific applications.

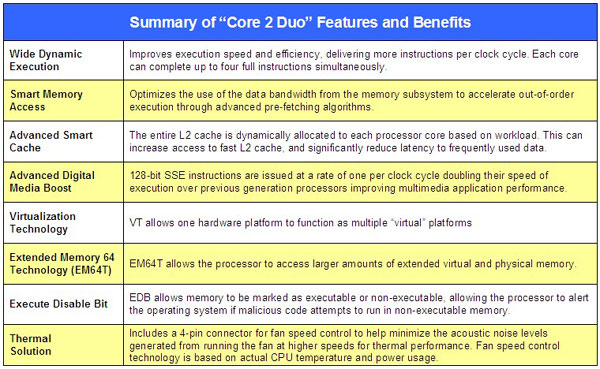

Summary of Core 2 Duo Features and Benefits

Intel is also stressing that great care has been taken to improve energy efficiency and various measures summarized as intelligent power capability have been implemented to reduce power consumption. We will explore these details when we discuss our findings about Conroes power consumption and heat output later in the article.

|

|

Advertisement:

All original content copyright James Rolfe.

All rights reserved. No reproduction allowed without written permission.

Interested in advertising on OCAU? Contact us for info.

|

|